题目:

Create a set of counters suitable for use as a 12-hour clock (with am/pm indicator). Your counters are clocked by a fast-running clk, with a pulse on ena whenever your clock should increment (i.e., once per second).

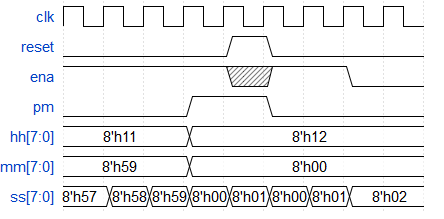

reset resets the clock to 12:00 AM. pm is 0 for AM and 1 for PM. hh, mm, and ss are two BCD (Binary-Coded Decimal) digits each for hours (01-12), minutes (00-59), and seconds (00-59). Reset has higher priority than enable, and can occur even when not enabled.

The following timing diagram shows the rollover behaviour from 11:59:59 AM to 12:00:00 PM and the synchronous reset and enable behaviour.

分析:实际上还是考察计数进位,需要注意的事pm反转是在11:59:59,刚开始以为是12:59:59呢,另外,我觉得8位的ss作为秒数的统计,我觉得不需要分低4位和高4位,那样反而麻烦,mm和hh也是如此。写的代码如下

代码:

module top_module(

input 最后

以上就是自觉豆芽最近收集整理的关于Verilog写一个时钟的全部内容,更多相关Verilog写一个时钟内容请搜索靠谱客的其他文章。

发表评论 取消回复