文章目录

- 24进制计数器设计要求

- 【 1. 源代码 】

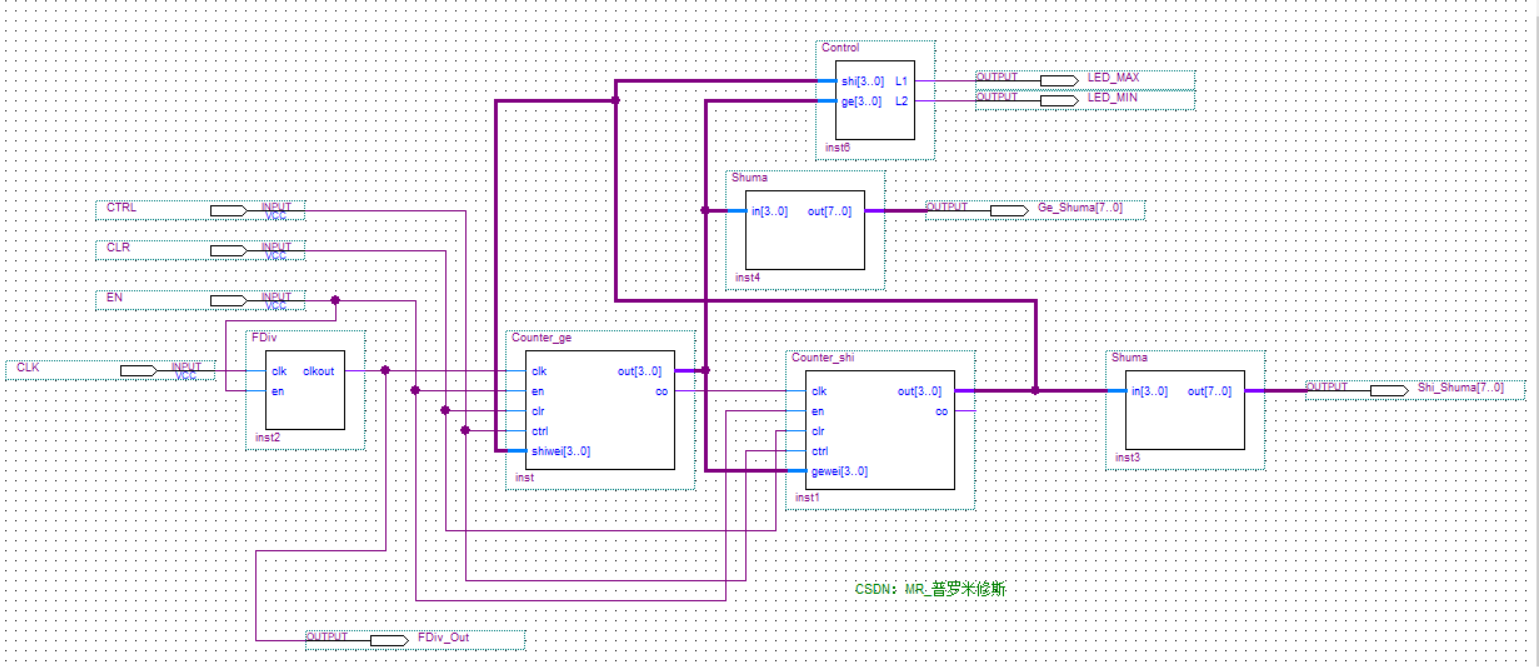

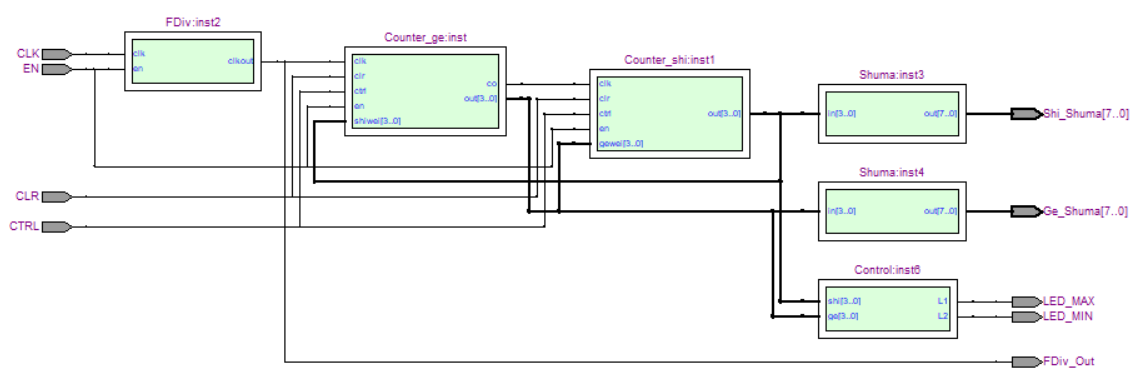

- 顶层文件

- 1. 分频器模块

- 2. 控制模块

- 3. 个位计数器模块

- 4. 十位计数器模块

- 5. 数码管模块

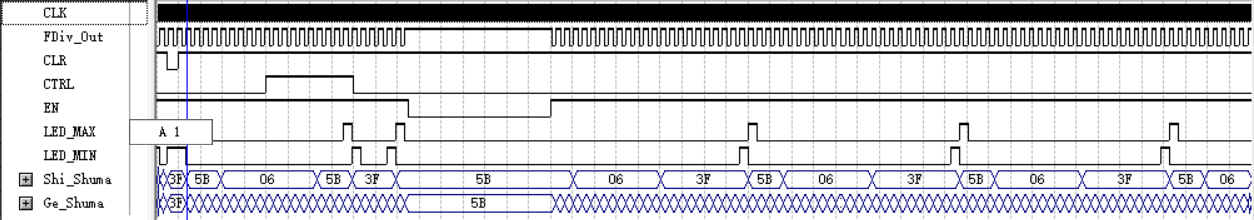

- 【 2. 仿真图 】

- 温故知新

24进制计数器设计要求

- 将4HZ信号分频得到的1HZ时钟信号作为计数脉冲。

- 具有加/减计数、开始/暂停计数、清零功能。

- 计数值通过两位数码管显示。

- 计数到最大值23、最小值0 时点亮LED,其他情况熄灭。

【 1. 源代码 】

顶层文件

1. 分频器模块

//N=4fen pin

module FDiv(clk,clkout,en);

input wire clk,en;

output reg clkout;

reg [3:0] q1;

always @ (posedge clk)

begin

if (en==1)

begin

q1=q1+1;

if(q1>=2) // N/2

begin

q1=0;

clkout=~clkout;

end

end

else

clkout=1;

end

endmodule

2. 控制模块

module Control(shi,ge,L1,L2);

input wire [3:0] shi,ge;

output reg L1,L2;

always@(shi,ge)

begin

if(shi==4'b0010 && ge==4'b0011) //max

L1=1;

else

L1=0;

if(shi==4'b00 && ge==4'b00)

L2=1;

else

L2=0;

end

endmodule

3. 个位计数器模块

module Counter_ge(clk,en,clr,ctrl,out,co,shiwei);

input clk,clr,ctrl,en;

input [3:0] shiwei;

output reg co;

output reg [3:0] out;

always@(posedge clk,negedge clr)

begin

if(!clr)

begin co<=0;out<=0; end

else

if(en)

begin

if(ctrl) //++

begin

if(out==3&&shiwei==2) begin out<=0;co<=1;end //加计数,到23

else if(out==9) begin out<=0;co<=1;end //09,19

else begin out<=out+4'b1;co<=0;end

end

else //--

begin

if(out==0&&shiwei==0) begin out<=3;co<=1;end //减计数,减到0

else if(out==0)begin out<=9;co<=1;end //20 10

else begin out=out-4'b1;co<=0;end

end

end

end

endmodule

4. 十位计数器模块

module Counter_shi(clk,en,clr,ctrl,out,co,gewei);

input clk,clr,ctrl,en;

input [3:0] gewei;

output reg co;

output reg [3:0] out;

always@(posedge clk,negedge clr)

begin

if(!clr)

begin co<=0;out<=0; end

else

if(en)

begin

if(ctrl) //++

begin

if(out==2&&gewei==0) begin out<=0;co<=1; end//十位out: 加计数,到23

else begin out<=out+4'b1;co<=0;end

end

else //--

begin

if(out==0&&gewei==3)begin out<=2;co<=1;end //十位out:减计数,减到0

else begin out=out-4'b1;co<=0;end

end

end

end

endmodule

5. 数码管模块

//共阴数码管

module Shuma(in,out);

input wire [3:0] in;

output reg [7:0] out;

always@(*)

begin

if(in==4'b0000) //0 0x3f

out<=8'b011_1111;

else if(in==4'b0001) //1 0x06

out<=8'b000_0110;

else if(in==4'b0010) //2 0x5b

out<=8'b101_1011;

else if(in==4'b0011) //3 0x4f

out<=8'b100_1111;

else if(in==4'b0100) //4 0x66

out<=8'b110_0110;

else if(in==4'b0101) //5 0x6d

out<=8'b110_1101;

else if(in==4'b0110) //6 0x7d

out<=8'b111_1101;

else if(in==4'b0111) //7 0x07

out<=8'b000_0111;

else if(in==4'b1000) //8 0x7f

out<=8'b111_1111;

else if(in==4'b1001) //9 0x6f

out<=8'b110_1111;

else if(in==4'b1010) //A 0x77

out<=8'b111_0111;

else if(in==4'b1011) //B 0x7c

out<=8'b111_1100;

else if(in==4'b1100) //C 0x39

out<=8'b011_1001;

else if(in==4'b1101) //D 0x5e

out<=8'b101_1110;

else if(in==4'b1110) //E 0x79

out<=8'b111_1001;

else if(in==4'b1111) //F 0x71

out<=8'b111_0001;

else

out<=8'b00;

end

endmodule

// code table[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

【 2. 仿真图 】

温故知新

24 进制计数器也可以通过一个 24的计数器 ( 从0计数到23 ),然后对计数值取余作为个位数,取商作为十位数而实现。·

最后

以上就是跳跃小熊猫最近收集整理的关于【Verilog HDL】24进制计数器【 1. 源代码 】【 2. 仿真图 】温故知新的全部内容,更多相关【Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复