QuartusII13.1 原理图编辑与仿真

上次写了一个用Verilog语言完成的半加器,这次就用原理图的方法做一个吧。

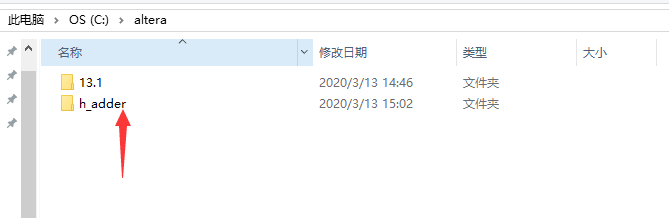

还是先新建一个文件夹:

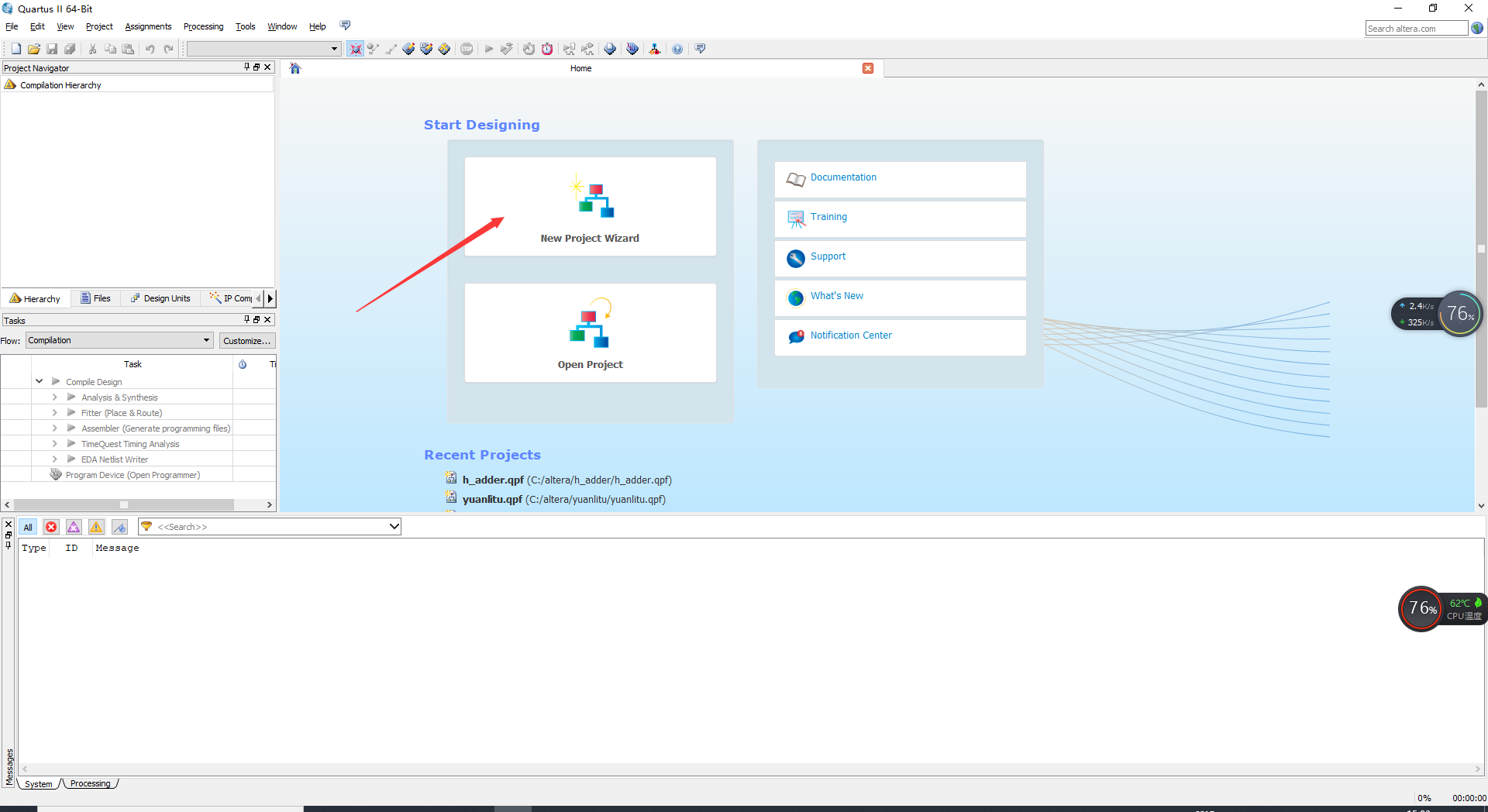

打开QuartusII,新建一个工程(也可以在file->new project wizard里新建):

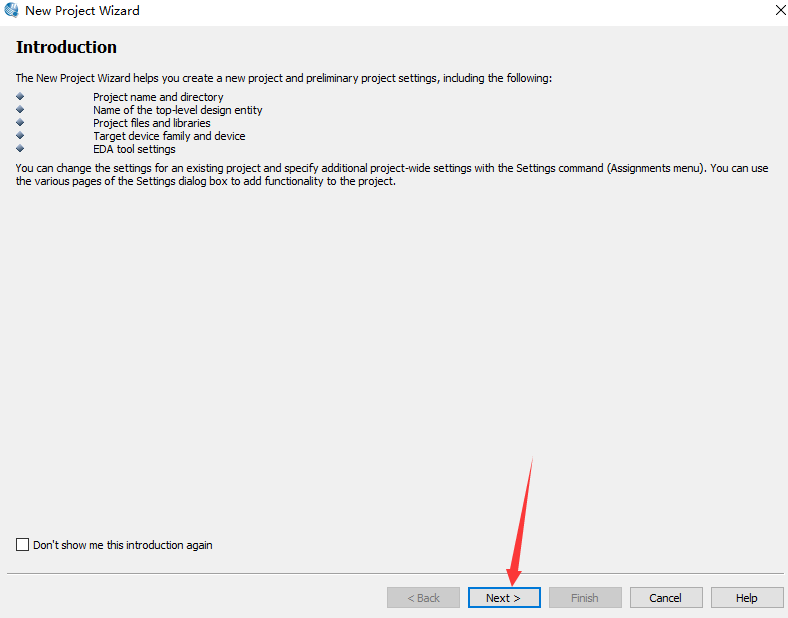

点击“Next”

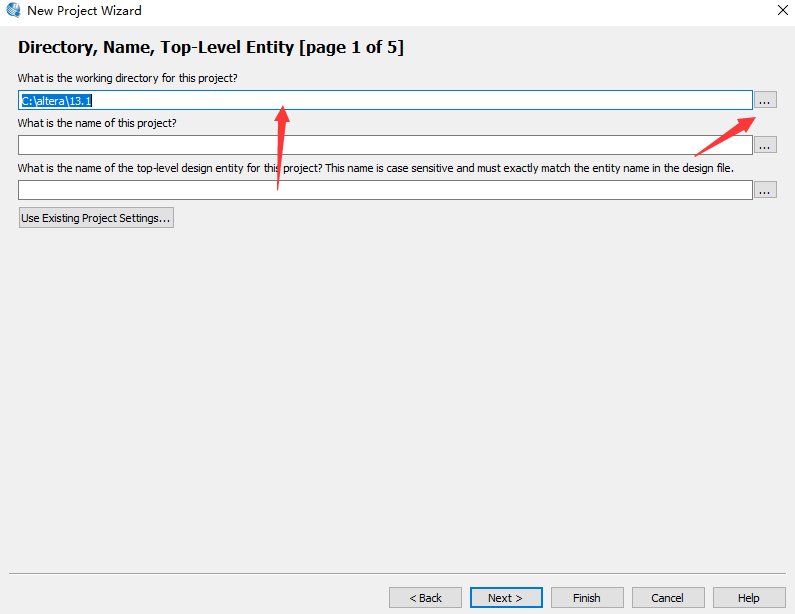

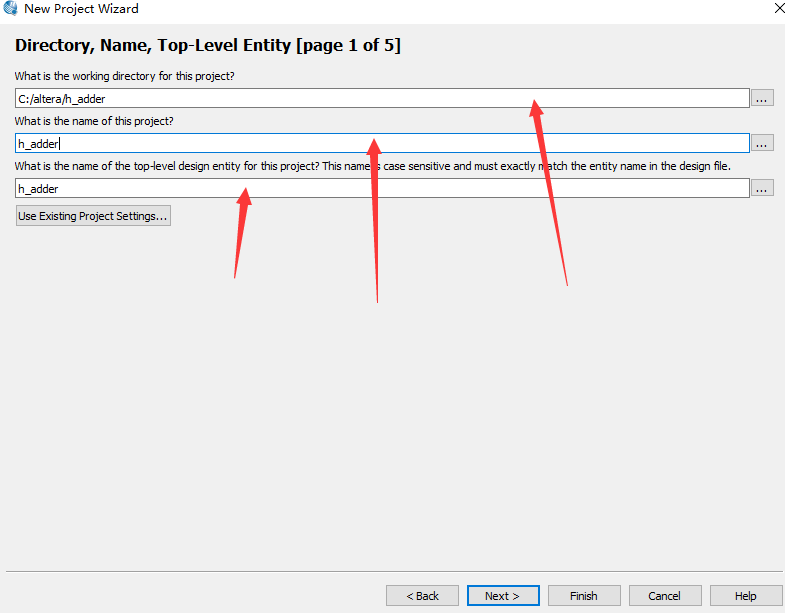

选择我们刚才新建的文件夹并加上工程名称和项目名称:

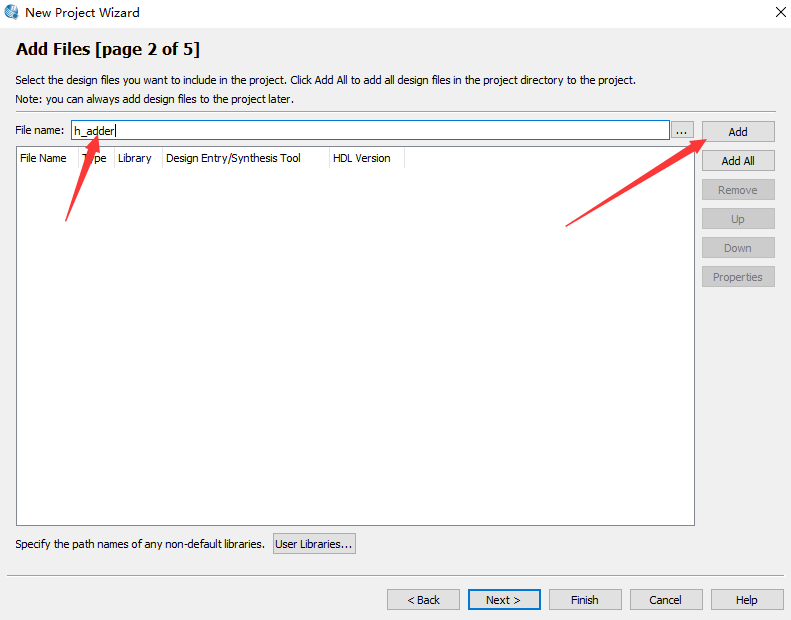

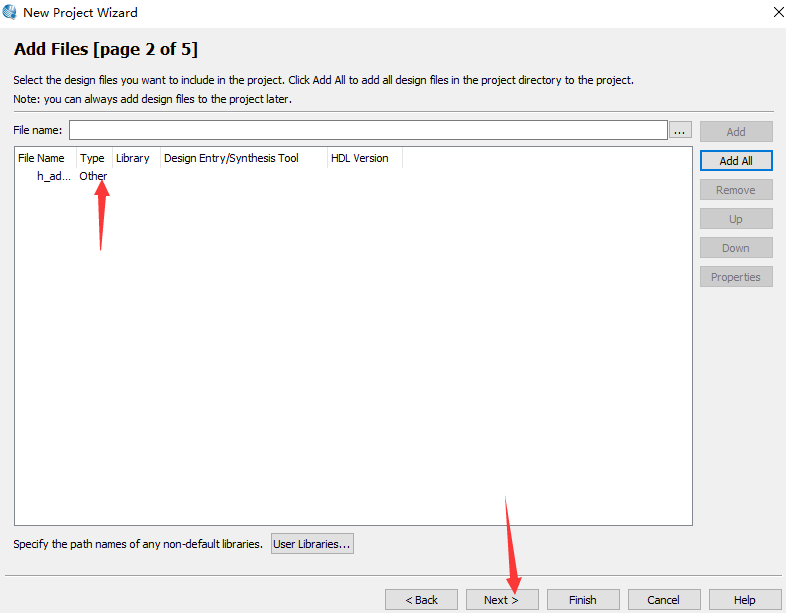

点击“Next”,为文件取一个名字并添加进来:

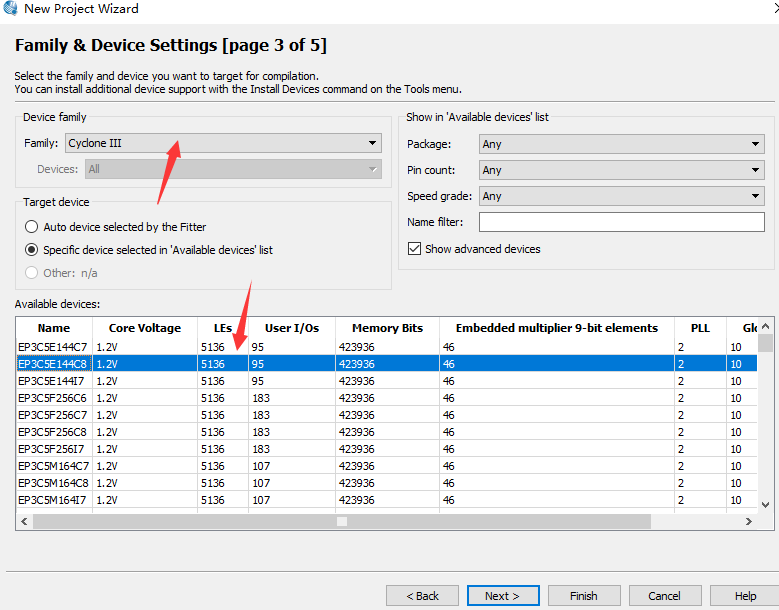

选择目标器件

看自己需要选择:

点击“Next”

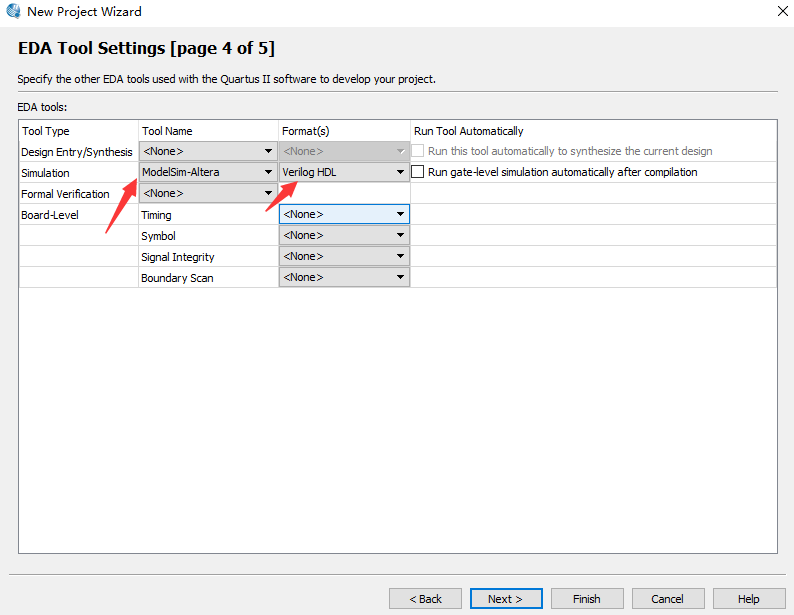

选择EDA工具(我这里好像选不选都行,但还是选上吧哈哈哈)

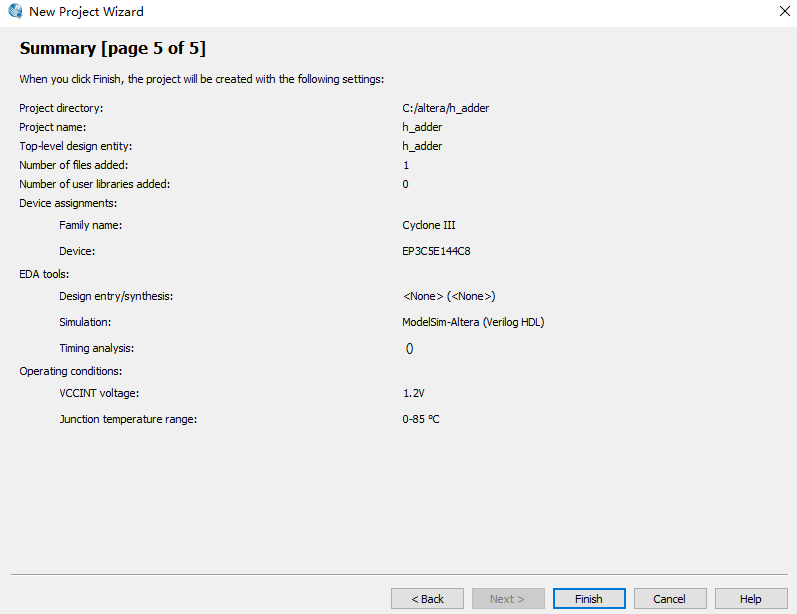

点击“Next”然后“Finish”

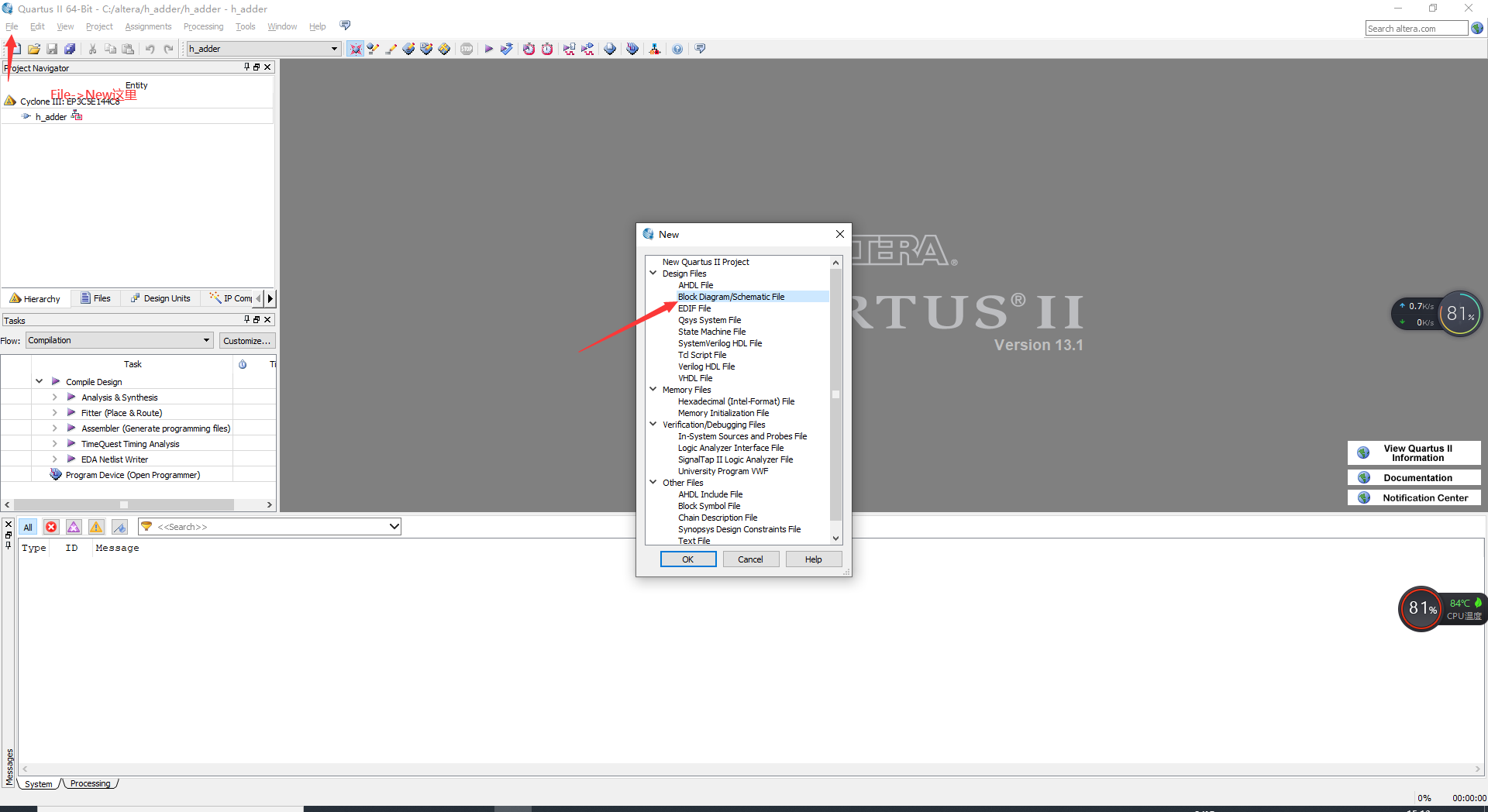

新建一个原理图:

好啦下面我们就可以在上面添加器件辣

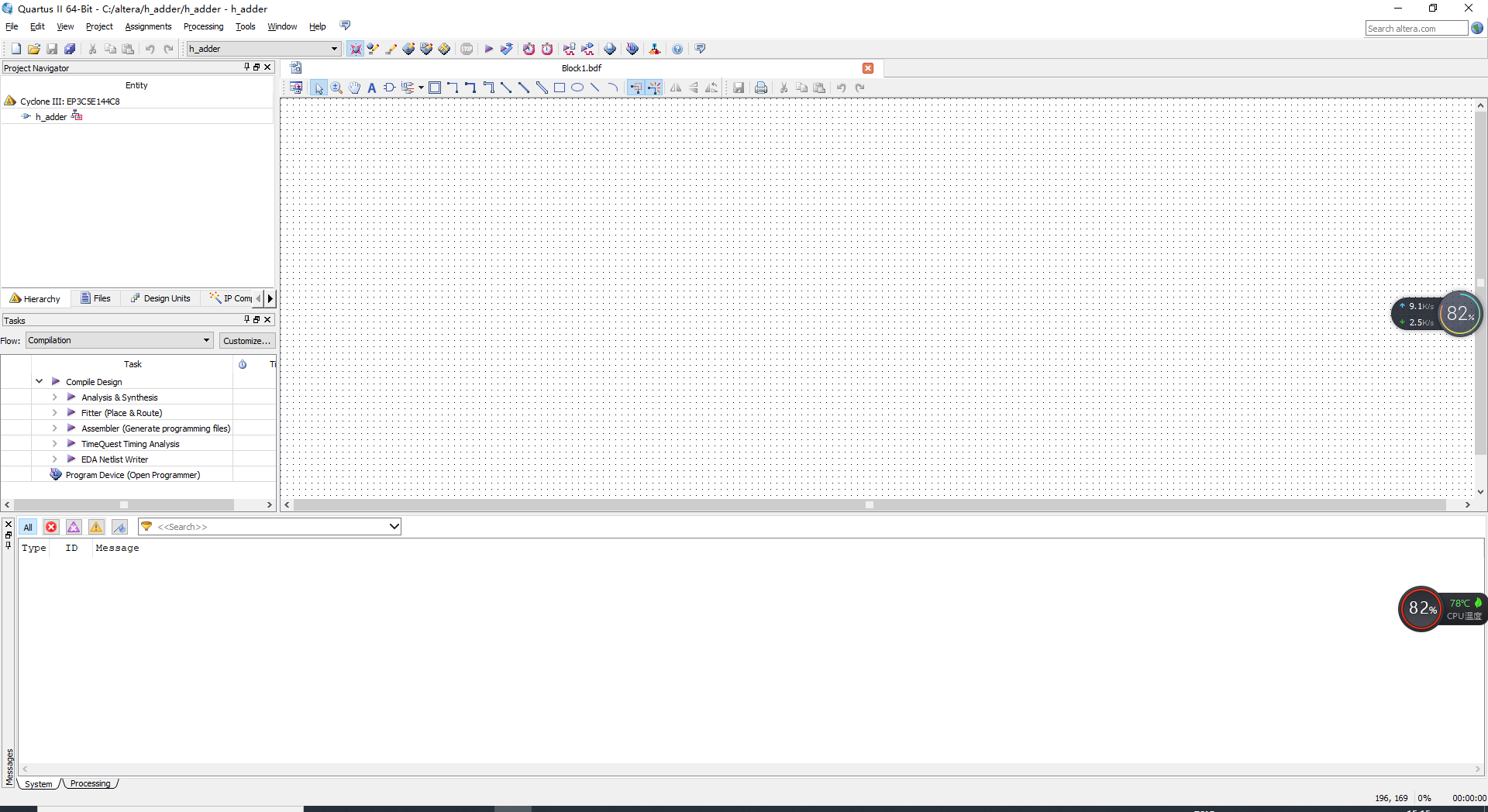

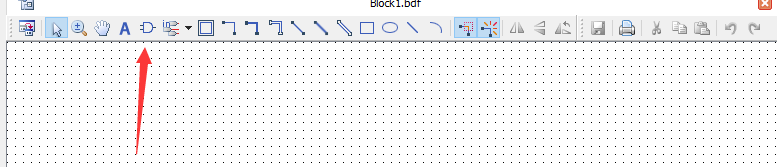

完成上一步的操作以后的页面:

添加器件可以双击“白板”,也可以点这里:

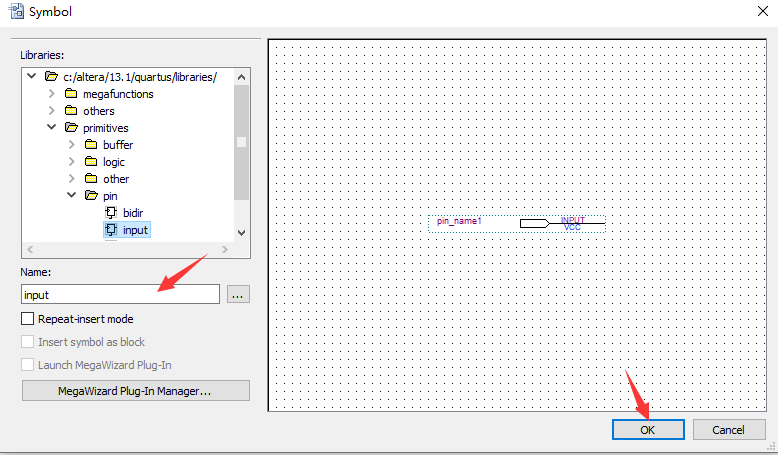

现在就在里面找需要的器件吧:

可以一个个找也可以自己输入查找:

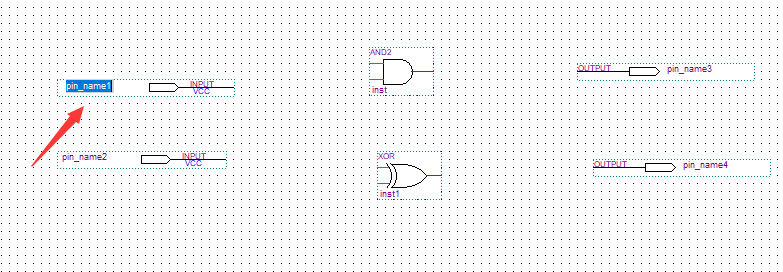

点击“OK”以后你的鼠标就会变成你想要的的器件啦,这时候就把需要的器件一一拖上去然后连起来就好啦

双击器件的默认的名字那里就可以改器件的名字啦:

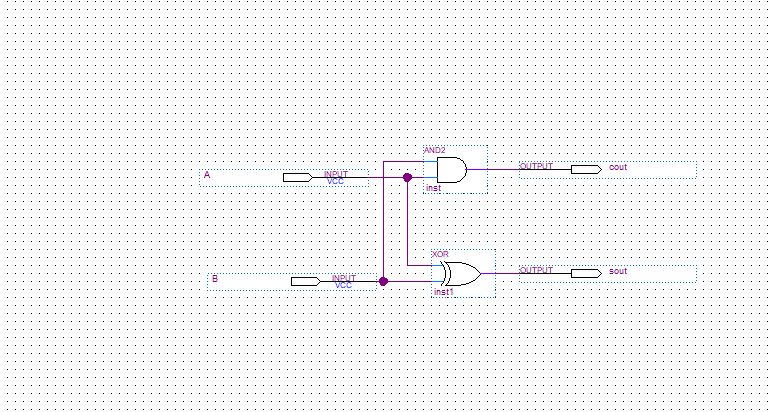

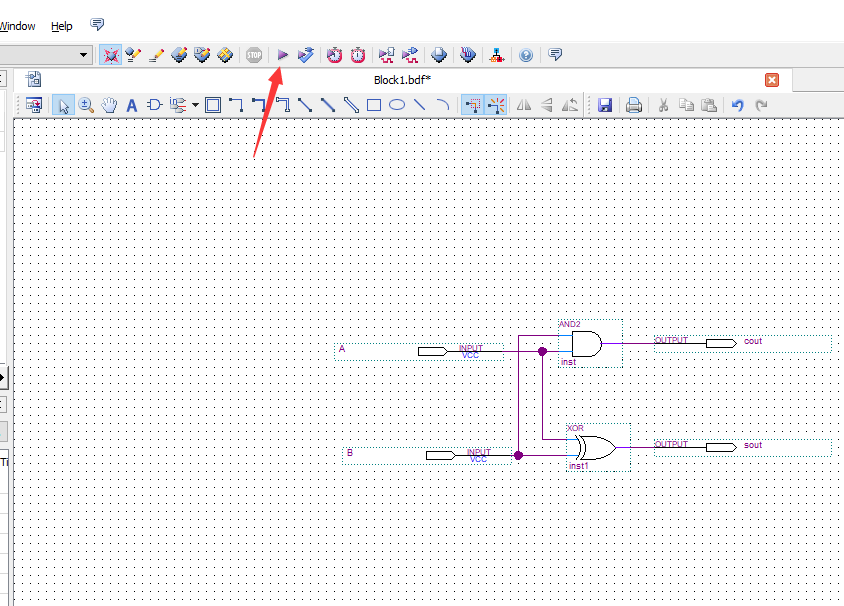

我就不再一个个演示啦,直接连好原理图啦 (轻大的亲们不知道原理图怎么连的可以参考课本58页哦~~):

下面开始编译:

点击这里(或者Processing->start complication):

弹出提示,点击“yes":

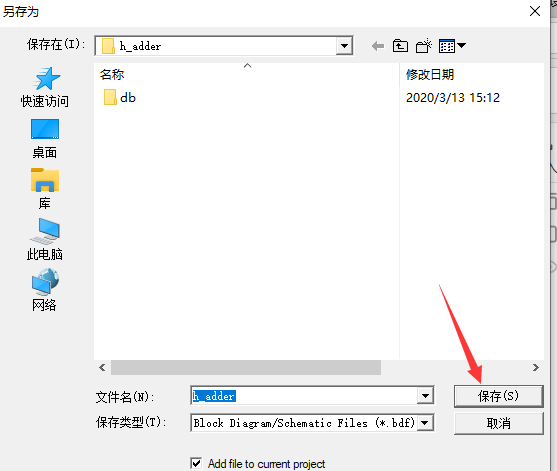

保存就好了:

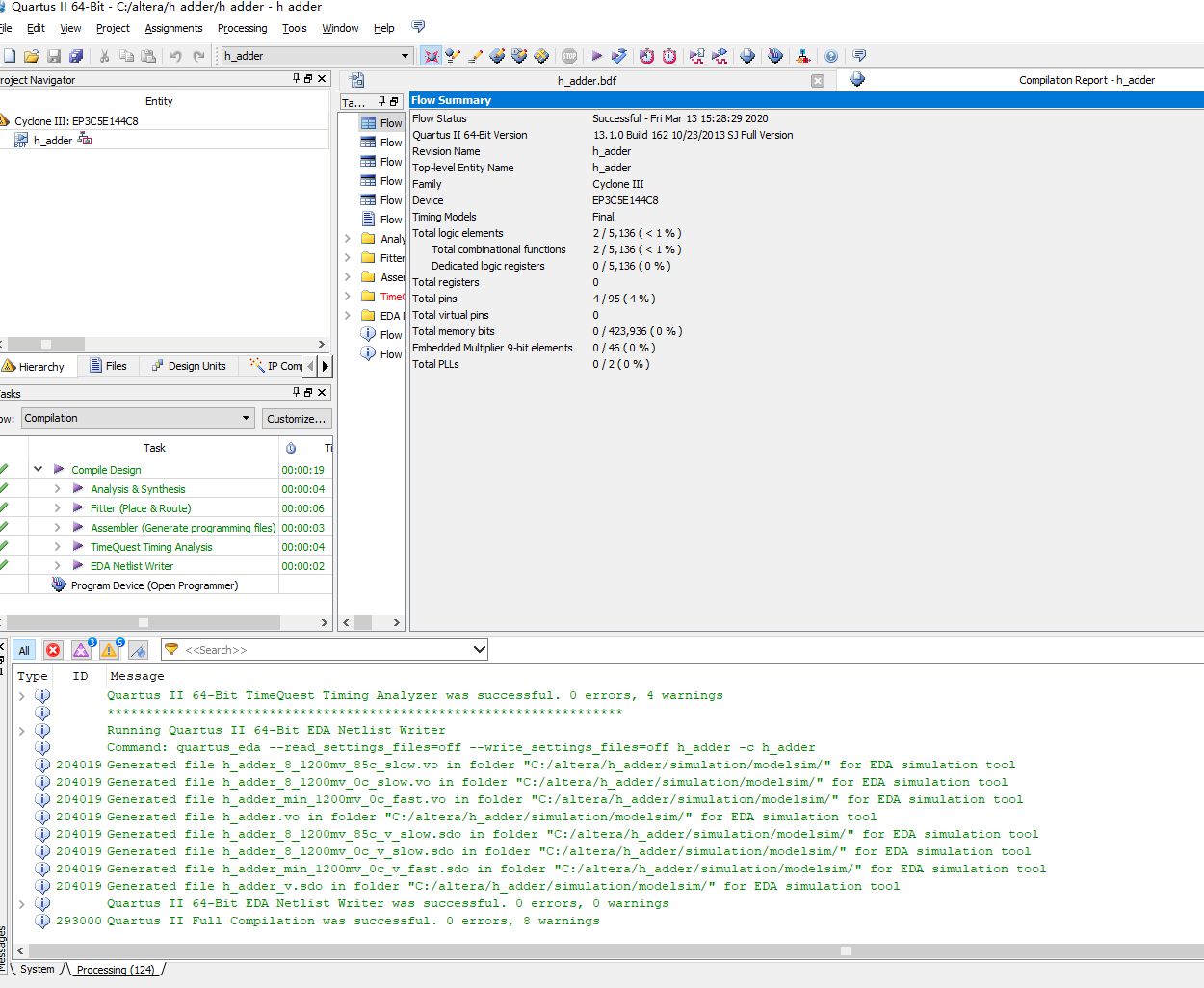

编译成功页面:

编译成功后我们就可以仿真啦

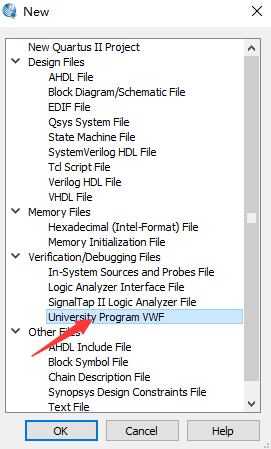

File–>New

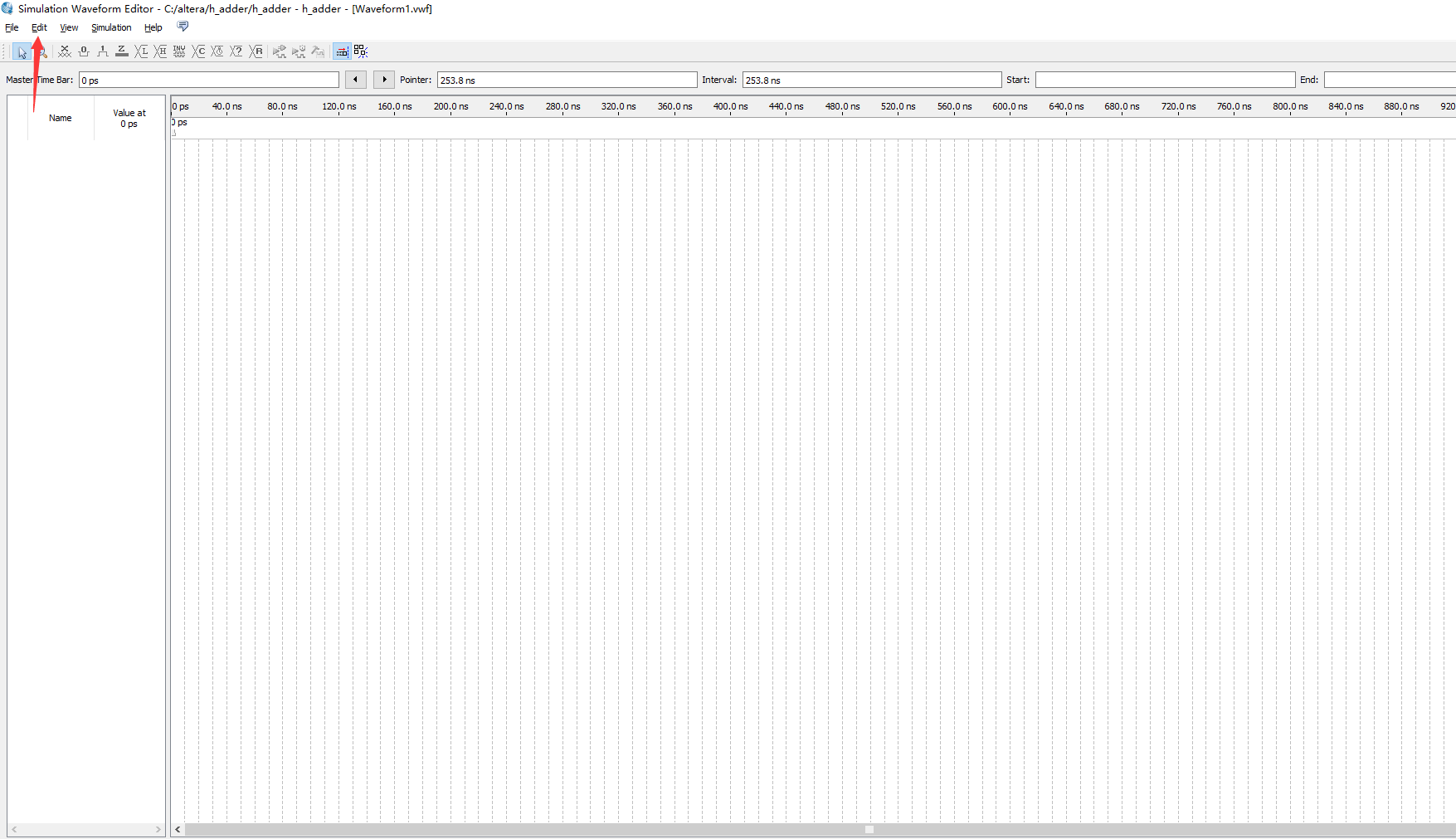

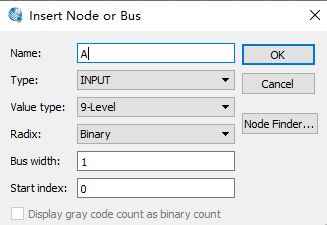

然后就出现了这个页面:

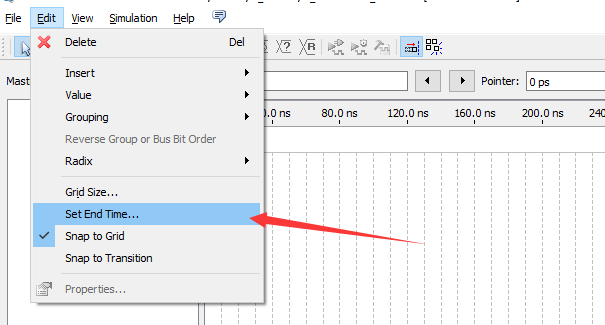

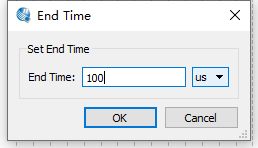

可以先设置一下终止时间:

这里我设置的是100us

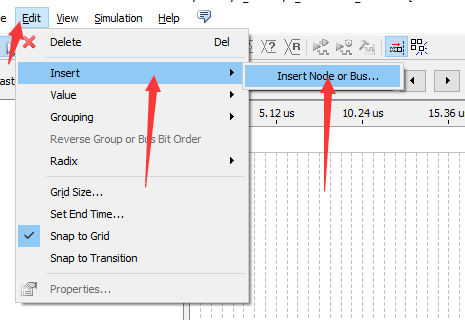

添加输入输出:

举个栗子:

都按照自己的输入输出来就行啦,记得类型改一下哦~:

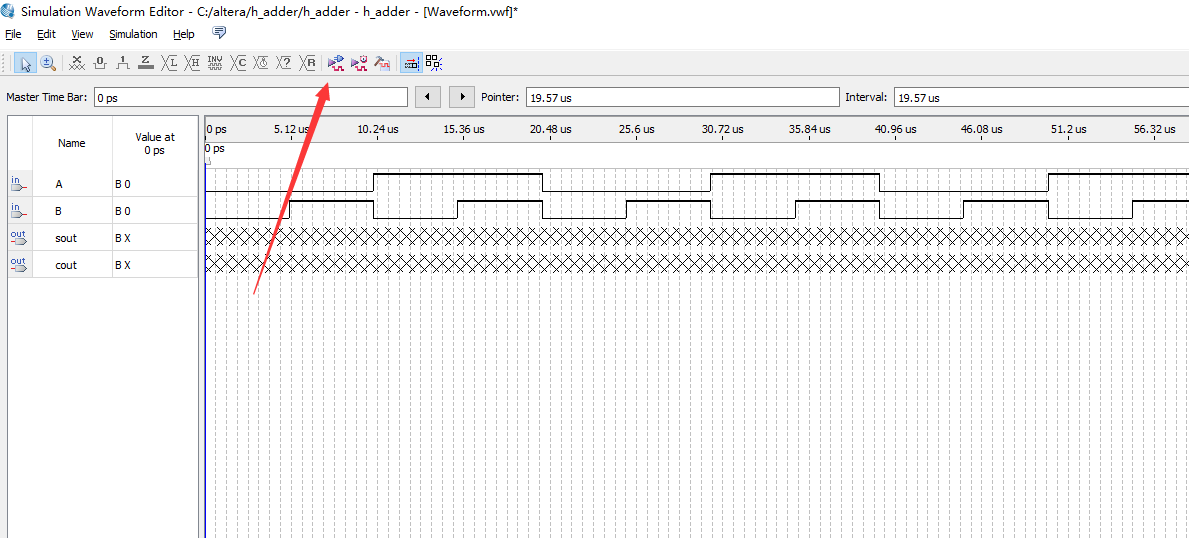

添加完以后的样子:

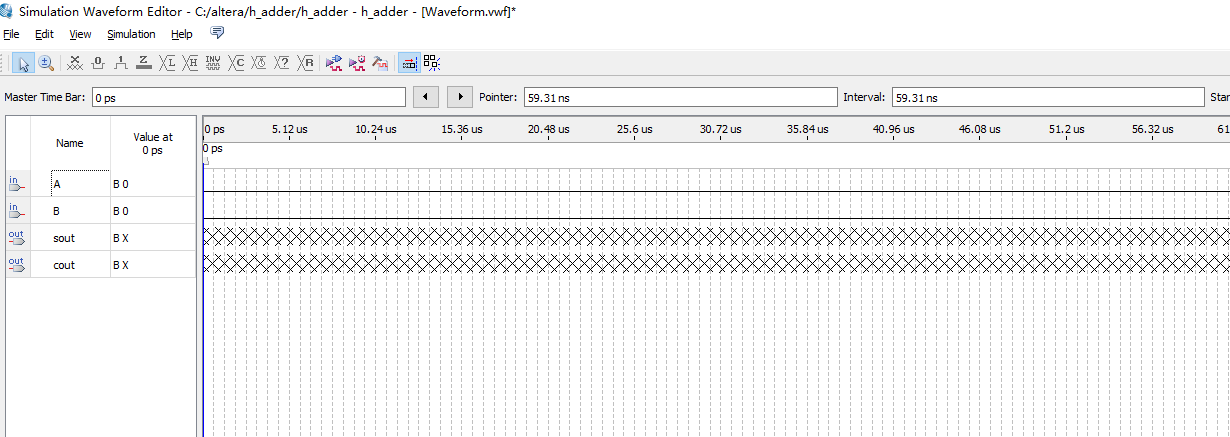

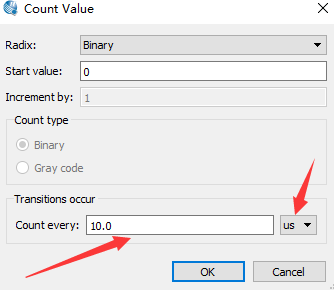

更改一下输入的波形:

根据自己的需要设置:

都设置好后就可以仿真了:

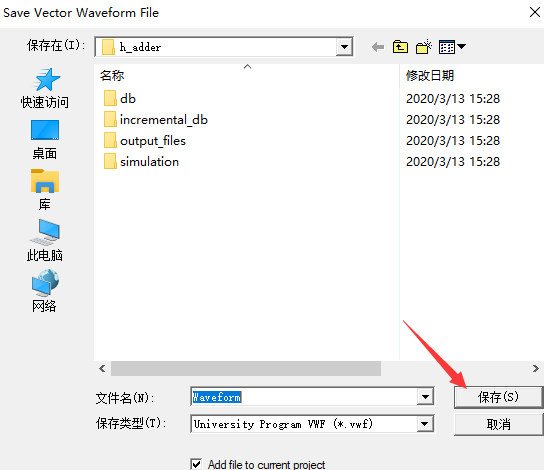

弹出一个小窗口,点击“也是”然后保存就可以了:

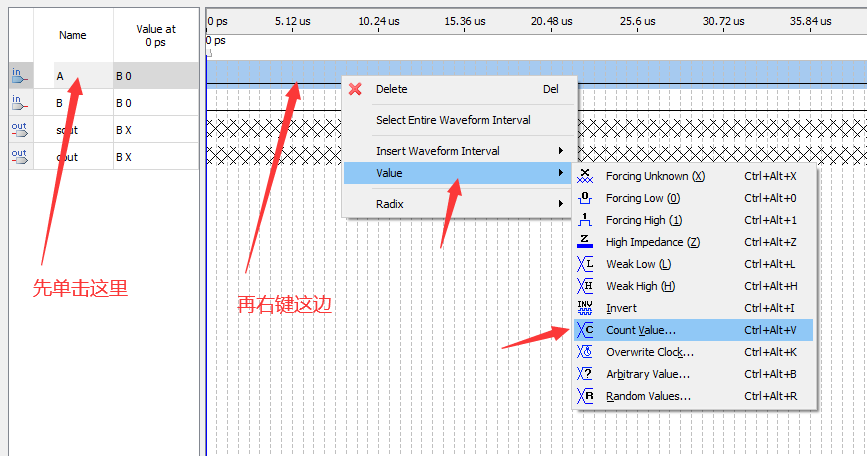

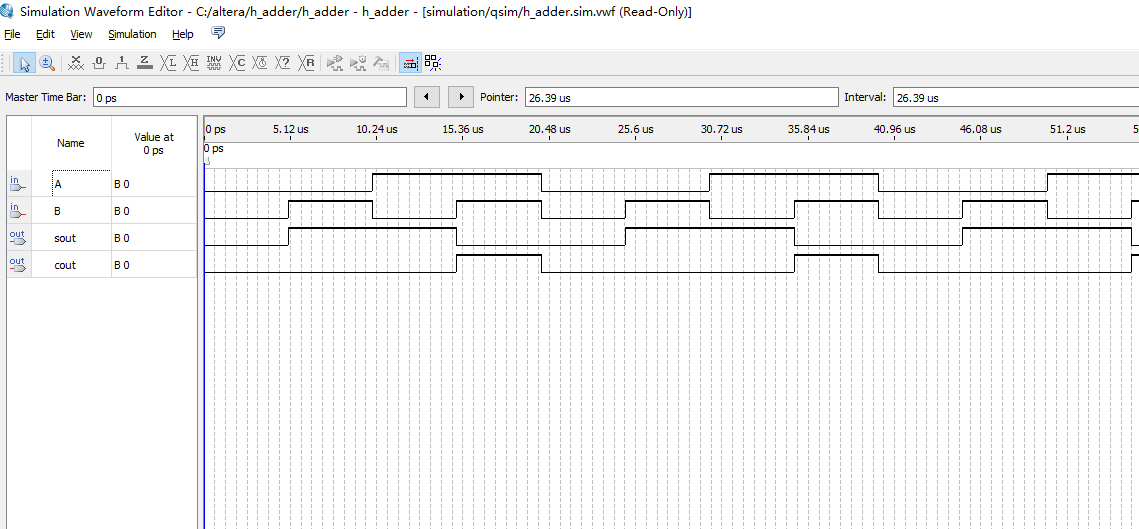

保存完以后等待编译一会就可以看见仿真的成功啦:

over~~

最后

以上就是深情星星最近收集整理的关于QuartusII13.1 原理图编辑与仿真(半加器为例)的全部内容,更多相关QuartusII13.1内容请搜索靠谱客的其他文章。

发表评论 取消回复