我是靠谱客的博主 开朗小刺猬,这篇文章主要介绍【74系列芯片的Verilog重现(一)】------74HC00【74系列芯片的Verilog重现(一)】------74HC00,现在分享给大家,希望可以做个参考。

【74系列芯片的Verilog重现(一)】------74HC00

【本工程基于Quartus16.1设计。】

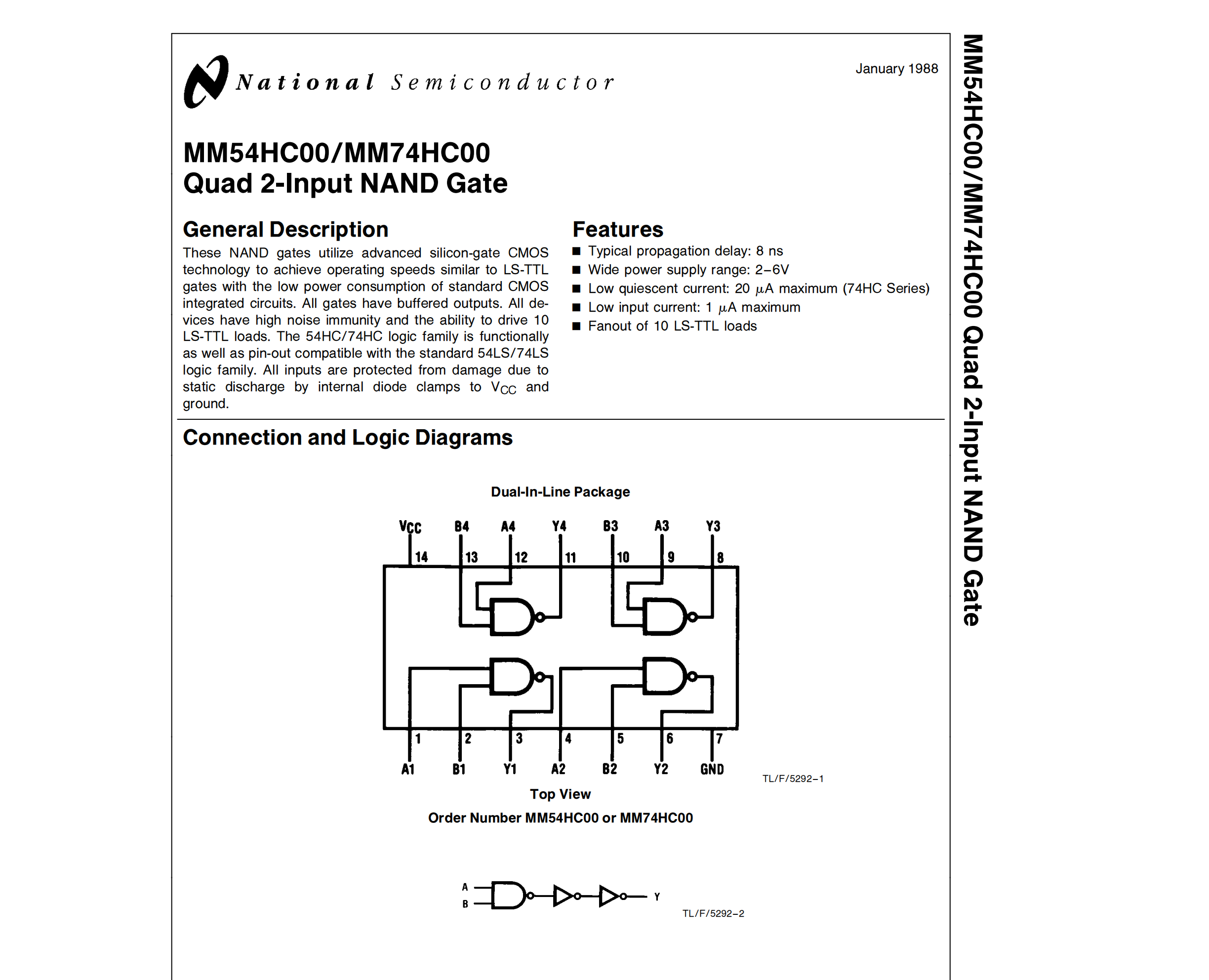

74HC00,是一款四通道两输入与非门。

源代码:

//74hc00

//Quad_2_Input_NAND_Gate

module Quad_2_Input_NAND_Gate

(

A1_1, B1_2, Y1_3,

A2_4, B2_5, Y2_6,

A3_8, B3_9, Y3_10,

A4_12, B4_13, Y4_11

);

input A1_1, B1_2, A2_4, B2_5,

A3_8, B3_9, A4_12, B4_13;

output Y1_3, Y2_6, Y3_10, Y4_11;

assign Y1_3 = ~( A1_1 & B1_2 ) ;

assign Y2_6 = ~( A2_4 & B2_5 ) ;

assign Y3_10 = ~( A3_8 & B3_9 ) ;

assign Y4_11 = ~( A4_12 & B4_13 ) ;

endmodule

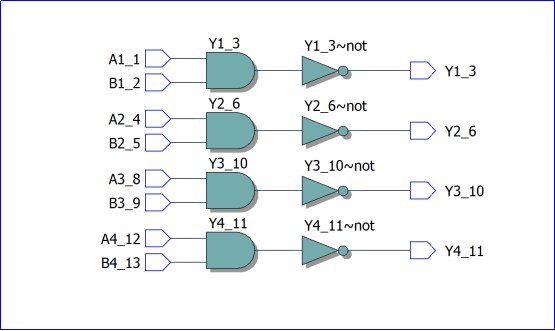

RTL视图:

仿真代码:

`timescale 1 ps/ 1 ps

module Quad_2_Input_NAND_Gate_vlg_tst();

reg A1_1;

reg A2_4;

reg A3_8;

reg A4_12;

reg B1_2;

reg B2_5;

reg B3_9;

reg B4_13;

// wires

wire Y1_3;

wire Y2_6;

wire Y3_10;

wire Y4_11;

// assign statements (if any)

Quad_2_Input_NAND_Gate i1 (

// port map - connection between master ports and signals/registers

.A1_1(A1_1),

.A2_4(A2_4),

.A3_8(A3_8),

.A4_12(A4_12),

.B1_2(B1_2),

.B2_5(B2_5),

.B3_9(B3_9),

.B4_13(B4_13),

.Y1_3(Y1_3),

.Y2_6(Y2_6),

.Y3_10(Y3_10),

.Y4_11(Y4_11)

);

initial

begin

A1_1 =0 ;

B1_2 =0 ;

A2_4 =0 ;

B2_5 =1 ;

A3_8 =1 ;

B3_9 =0 ;

A4_12 =1 ;

B4_13 =1 ;

#100

A1_1 =0 ;

B1_2 =1 ;

A2_4 =0 ;

B2_5 =0 ;

A3_8 =1 ;

B3_9 =0 ;

A4_12 =1 ;

B4_13 =1 ;

#100 $stop;

$display("Running testbench");

end

endmodule

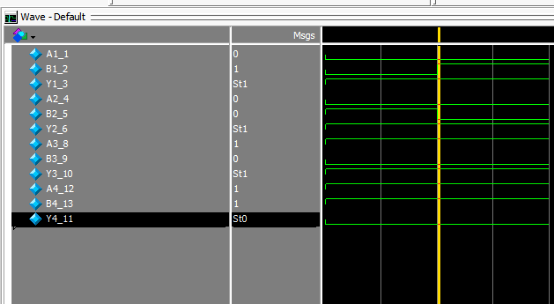

仿真结果:

工程文件:

[文件] 01_74HC00.zip 工程文件分享

最后

以上就是开朗小刺猬最近收集整理的关于【74系列芯片的Verilog重现(一)】------74HC00【74系列芯片的Verilog重现(一)】------74HC00的全部内容,更多相关【74系列芯片内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复