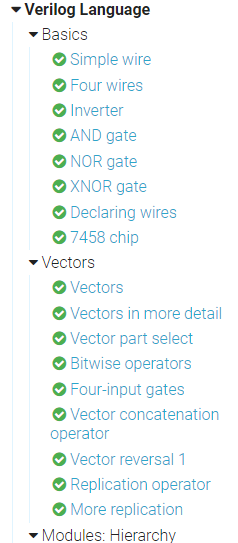

最近发现一个很有意思的网站,可以在线提交 verilog 代码以完成一些任务,并且还能得到仿真结果对比。可以利用零碎时间提交一些代码,练习verilog基础知识。

网址如下:

https://hdlbits.01xz.net/wiki/

从 basics 开始对提交的答案进行汇总。(本博客会不断更新)

//03_Wire.v

module top_module( input in, output out );

assign out = in;

endmodule

//04_Wire4.v

module top_module(

input a,b,c,

output w,x,y,z );

assign w = a;

assign x = b;

assign y = b;

assign z = c;

endmodule

//05_Inverter.v

module top_module( input in, output out );

assign out = ~in;

endmodule

//06_Andgate.v

module top_module(

input a,

input b,

output out );

assign out = a & b;

endmodule

//07_Norgate.v

module top_module(

input a,

input b,

output out );

assign out = ~(a | b);

endmodule

//08_Xnorgate.v

module top_module(

input a,

input b,

output out );

assign out = ~(a ^ b);

endmodule

//09_Wire_decl.v

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire wire1, wire2, wire3;

assign wire1 = a & b;

assign wire2 = c & d;

assign wire3 = wire1 | wire2;

assign out = wire3;

assign out_n = ~wire3;

endmodule

//10_7458.v

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire abc1, def1, ab2, cd2;

assign abc1 = p1c & p1b & p1a;

assign def1 = p1f & p1e & p1d;

assign p1y = abc1 | def1;

assign ab2 = p2a & p2b;

assign cd2 = p2c & p2d;

assign p2y = ab2 | cd2;

endmodule

//11_Vector0.v

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

assign outv = vec;

assign o0 = outv[0];

assign o1 = outv[1];

assign o2 = outv[2];

endmodule

//12_7Vector1.v

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule

//13_Vector2.v

module top_module(

input [31:0] in,

output [31:0] out );//

// assign out[31:24] = ...;

assign out = {in[7:0], in[15:8], in[23:16], in[31:24]};

endmodule

//14_Vectorgates.v

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a | b;

assign out_or_logical = a || b;

assign out_not[5:3] = ~b;

assign out_not[2:0] = ~a;

endmodule

//15_Gates4.v

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = in[0] & in[1] & in[2] & in[3];

assign out_or = in[0] | in[1] | in[2] | in[3];

assign out_xor = in[0] ^ in[1] ^ in[2] ^ in[3];

endmodule

//16_Vector3.v

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

// assign { ... } = { ... };

// assign {w[7:0], x[7:0], y[7:0], z[7:0]} = {a[4:0], b[4:0], c[4:0], d[4:0], e[4:0], f[4:0], 2'b11};

assign {w, x, y, z} = {a, b, c, d, e, f, 2'b11};

endmodule

//17_Vectorr.v

module top_module(

input [7:0] in,

output [7:0] out

);

assign out = {in[0], in[1], in[2], in[3], in[4], in[5], in[6], in[7]};

endmodule

//18_Vector4.v

module top_module (

input [7:0] in,

output [31:0] out );//

// assign out = { replicate-sign-bit , the-input };

assign out = {{24{in[7]}}, in};

endmodule

//19_Vector5.v

module top_module (

input a, b, c, d, e,

output [24:0] out );//

assign out[24:20] = ~ {5{a}} ^ {a, b, c, d, e};

assign out[19:15] = ~ {5{b}} ^ {a, b, c, d, e};

assign out[14:10] = ~ {5{c}} ^ {a, b, c, d, e};

assign out[9:5] = ~ {5{d}} ^ {a, b, c, d, e};

assign out[4:0] = ~ {5{e}} ^ {a, b, c, d, e};

endmodule

//20_Module.v

module top_module ( input a, input b, output out );

mod_a instance1(.out(out), .in1(a), .in2(b));

endmodule

//21_Module_pos.v

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a instance1(out1, out2, a, b, c, d);

endmodule

//22_Module_name.v

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a instance1(.in1(a), .in2(b), .in3(c), .in4(d), .out1(out1), .out2(out2),);

endmodule

//23_Module_shift.v

module top_module ( input clk, input d, output q );

wire q1, q2;

my_dff instance1(.clk(clk), .d(d), .q(q1));

my_dff instance2(.clk(clk), .d(q1), .q(q2));

my_dff instance3(.clk(clk), .d(q2), .q(q));

endmodule

//24_Module_shift8v.v

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0] q1, q2, q3;

my_dff8 instance1(.clk(clk), .d(d), .q(q1));

my_dff8 instance2(.clk(clk), .d(q1), .q(q2));

my_dff8 instance3(.clk(clk), .d(q2), .q(q3));

always @(*) begin

case(sel)

0 : q = d;

1 : q = q1;

2 : q = q2;

3 : q = q3;

endcase

end

endmodule

//25_Module_add.v

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cin1, cout1,cout2;

wire [15:0] sum1, sum2;

assign cin1 = 0;

add16 instance1(.a(a[15:0]), .b(b[15:0]), .cin(cin1), .cout(cout1), .sum(sum1));

add16 instance2(.a(a[31:16]), .b(b[31:16]), .cin(cout1), .cout(cout2), .sum(sum2));

assign sum = {sum2, sum1};

endmodule

//26_Module_fadd.v

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);//

wire cin1, cout1, cout2;

wire [15:0] sum1, sum2;

assign cin1 = 0;

add16 instance1(.a(a[15:0]), .b(b[15:0]), .cin(cin1), .cout(cout1), .sum(sum1));

add16 instance2(.a(a[31:16]), .b(b[31:16]), .cin(cout1), .cout(cout2), .sum(sum2));

assign sum = {sum2, sum1};

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

// Full adder module here

always @(*) begin

if(!cin) begin

if(a == 0 && b == 0) begin

sum = 0;

cout = 0;

end

else if((a == 0 && b == 1) || (a == 1 && b == 0)) begin

sum = 1;

cout = 0;

end

else begin

sum = 0;

cout = 1;

end

end

else begin

if(a == 0 && b == 0) begin

sum = 1;

cout = 0;

end

else if((a == 0 && b == 1) || (a == 1 && b == 0)) begin

sum = 0;

cout = 1;

end

else begin

sum = 1;

cout = 1;

end

end

end

endmodule

//27_Module_cseladd.v

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cin1, cout1, cin2, cout2, cin3, cout3;

wire [15:0] sum1, sum2, sum3, sum_h;

assign cin1 = 0;

assign cin2 = 0;

assign cin3 = 1;

add16 instance1(.a(a[15:0]), .b(b[15:0]), .cin(cin1), .cout(cout1), .sum(sum1));

add16 instance2(.a(a[31:16]), .b(b[31:16]), .cin(cin2), .cout(cout2), .sum(sum2));

add16 instance3(.a(a[31:16]), .b(b[31:16]), .cin(cin3), .cout(cout3), .sum(sum3));

always @(*) begin

case(cout1)

0 : sum_h = sum2;

1 : sum_h = sum3;

endcase

end

assign sum = {sum_h, sum1};

endmodule

//28_Module_addsub.v

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] result

);

wire cout1, cout2;

wire [15:0] sum1, sum2;

wire [31:0] b_xor;

always @(*) begin

if(sub)

b_xor = ~b;

else

b_xor = b;

end

add16 instance1(.a(a[15:0]), .b(b_xor[15:0]), .cin(sub), .cout(cout1), .sum(sum1));

add16 instance2(.a(a[31:16]), .b(b_xor[31:16]), .cin(cout1), .cout(cout2), .sum(sum2));

assign result = {sum2, sum1};

endmodule

//29_Alwaysblock1.v

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign = a & b;

always @(*) out_alwaysblock = a & b;

endmodule

//30_Alwaysblock2.v

// synthesis verilog_input_version verilog_2001

module top_module(

input clk,

input a,

input b,

output wire out_assign,

output reg out_always_comb,

output reg out_always_ff );

assign out_assign = a ^ b;

always @(*) out_always_comb = a ^ b;

always @(posedge clk) out_always_ff <= a ^ b;

endmodule

//31_Always if.v

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

input sel_b1,

input sel_b2,

output wire out_assign,

output reg out_always );

assign out_assign = (sel_b1 && sel_b2) ? b : a;

always @(*) out_always = (sel_b1 && sel_b2) ? b : a;

endmodule

//32_Always if2.v

// synthesis verilog_input_version verilog_2001

module top_module (

input cpu_overheated,

output reg shut_off_computer,

input arrived,

input gas_tank_empty,

output reg keep_driving ); //

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

else

shut_off_computer = 0;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

else

keep_driving = 0;

end

endmodule

//33_Always_case.v

// synthesis verilog_input_version verilog_2001

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

0 : out = data0;

1 : out = data1;

2 : out = data2;

3 : out = data3;

4 : out = data4;

5 : out = data5;

default : out = 0;

endcase

end

endmodule

//34 Always case2

// synthesis verilog_input_version verilog_2001

module top_module (

input [3:0] in,

output reg [1:0] pos );

integer i;

always@(*)

begin

case(in)

4'd0 : pos = 0;

4'd1 : pos = 0;

4'd2 : pos = 1;

4'd3 : pos = 0;

4'd4 : pos = 2;

4'd5 : pos = 0;

4'd6 : pos = 1;

4'd7 : pos = 0;

4'd8 : pos = 3;

4'd9 : pos = 0;

4'd10 : pos = 1;

4'd11 : pos = 0;

4'd12 : pos = 2;

4'd13 : pos = 0;

4'd14 : pos = 1;

4'd15 : pos = 0;

endcase

end

endmodule

// 35 Always casez

// synthesis verilog_input_version verilog_2001

module top_module (

input [7:0] in,

output reg [2:0] pos );

always @ (*)

begin

casez(in)

8'bzzzzzzz1: pos = 3'd0;

8'bzzzzzz1z: pos = 3'd1;

8'bzzzzz1zz: pos = 3'd2;

8'bzzzz1zzz: pos = 3'd3;

8'bzzz1zzzz: pos = 3'd4;

8'bzz1zzzzz: pos = 3'd5;

8'bz1zzzzzz: pos = 3'd6;

8'b1zzzzzzz: pos = 3'd7;

default: pos = 3'd0;

endcase

end

endmodule

//36 Always nolatches

// synthesis verilog_input_version verilog_2001

module top_module (

input [15:0] scancode,

output reg left,

output reg down,

output reg right,

output reg up );

always@(*)

begin

case(scancode)

16'he06b:

begin

left = 1;

down = 0;

right = 0;

up = 0;

end

16'he072:

begin

left = 0;

down = 1;

right = 0;

up = 0;

end

16'he074:

begin

left = 0;

down = 0;

right = 1;

up = 0;

end

16'he075:

begin

left = 0;

down = 0;

right = 0;

up = 1;

end

default:

begin

left = 0;

down = 0;

right = 0;

up = 0;

end

endcase

end

endmodule

最后

以上就是魔幻海燕最近收集整理的关于hdlbits 练习汇总的全部内容,更多相关hdlbits内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复