3.2组合逻辑电路的应用

常用的组合逻辑电路有编码器、译码器、数据选择器、数值比较器和加法器等,下面介绍一下这些常用电路的工作原理和使用方法。

3.2.1、编码器

各种遥控器、密码输入都属于编码器,编码器有互斥编码器和优先编码器之分。

互斥编码器:任何时刻只允许一个输入信号有效,否则将产生错误输出。

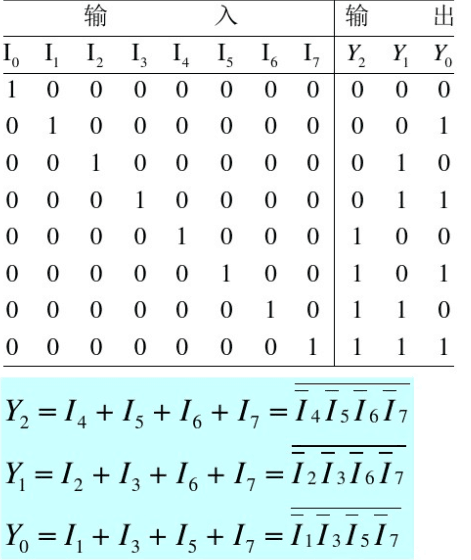

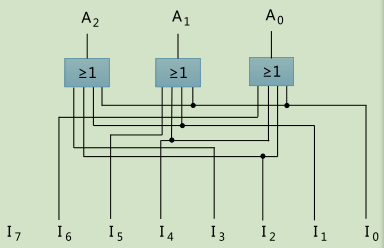

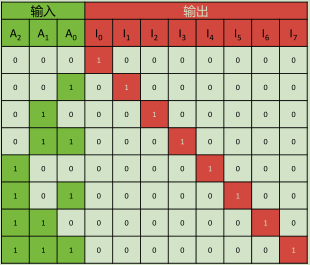

以8-3互斥编码器为例,所谓8-3编码器就是实现三位二进制代码对八个信号进行编码的电路,对应着8个输入和3个输出。由此写出真值表如图所示,真值表转换成表达式的方法:将输出为1的几个变量相加,如图所示的真值表转换成表达式为:

根据真值表画出电路图如图所示:

verilog代码如下所示:

//---------------------------------------------------------------------------

//-- 文件名 : Digital_Encoder.v

//-- 作者 : ZIRCON

//-- 描述 : 编码器模块

//-- 修订历史 : 2017-1-1

//---------------------------------------------------------------------------

module Digital_Encoder

(

/* 输入端口 */

I,

/* 输出端口 */

A

);

//---------------------------------------------------------------------------

//-- 外部端口声明

//---------------------------------------------------------------------------

input [7:0] I; //输入端口

output [2:0] A; //输出端口

//---------------------------------------------------------------------------

//-- 内部端口声明

//---------------------------------------------------------------------------

reg [2:0] A; //输入端口

//---------------------------------------------------------------------------

//-- 逻辑功能实现

//---------------------------------------------------------------------------

/* 组合电路,实现编码器 */

always @ (*)

begin

case(I)

8'b0000_0001 : A = 3'b000;

8'b0000_0010 : A = 3'b001;

8'b0000_0100 : A = 3'b010;

8'b0000_1000 : A = 3'b011;

8'b0001_0000 : A = 3'b100;

8'b0010_0000 : A = 3'b101;

8'b0100_0000 : A = 3'b110;

8'b1000_0000 : A = 3'b111;

default: A = 3'b000;

endcase

end

endmodule

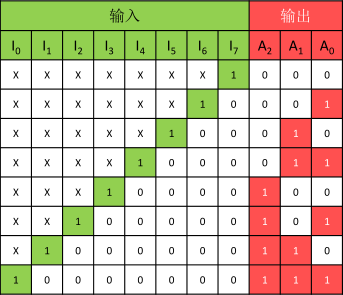

优先编码器:允许多个输入信号同时有效,输出是对优先级别高的输入信号进行编码。

verilog代码为:

//---------------------------------------------------------------------------

//-- 文件名 : Digital_Priority_Encoder.v

//-- 作者 : ZIRCON

//-- 描述 : 优先编码器模块

//-- 修订历史 : 2017-1-1

//---------------------------------------------------------------------------

module Digital_Priority_Encoder

(

/* 输入端口 */

I,

/* 输出端口 */

A

);

//---------------------------------------------------------------------------

//-- 外部端口声明

//---------------------------------------------------------------------------

input [7:0] I; //输入端口

output [2:0] A; //输出端口

//---------------------------------------------------------------------------

//-- 内部端口声明

//---------------------------------------------------------------------------

reg [2:0] A; //输出端口

//---------------------------------------------------------------------------

//-- 逻辑功能实现

//---------------------------------------------------------------------------

/* 组合电路,实现优先编码器 */

always @ (*)

begin

if(I[7] == 1'b0) A = 3'b000;

else if(I[6] == 1'b0) A = 3'b001;

else if(I[5] == 1'b0) A = 3'b010;

else if(I[4] == 1'b0) A = 3'b011;

else if(I[3] == 1'b0) A = 3'b100;

else if(I[2] == 1'b0) A = 3'b101;

else if(I[1] == 1'b0) A = 3'b110;

else if(I[0] == 1'b0) A = 3'b111;

else A = 3'b000;

end

endmodule

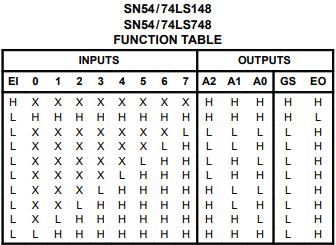

和前面的比较输入部分只要优先级高的(从I7到I0优先级从高到低),只要优先级高的为1后面的都不看了。常见的优先编码器有74LS148

3.2.2、译码器

译码器是编码器的逆过程,通常用于计算机中对存储单元的地址的译码。n个二进制选择线的译码器最多可译码转换成2^n个数据。

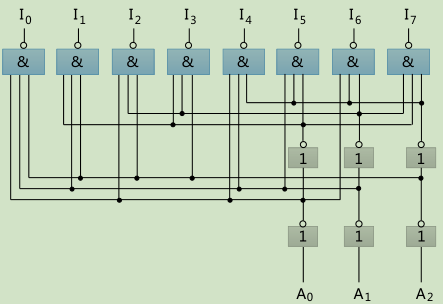

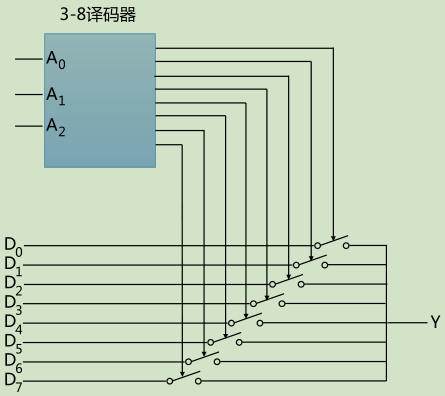

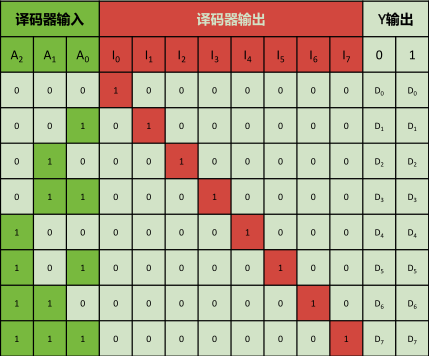

以3-8译码器为例,有3个输入,8个输出,3-8译码器的真值表如图所示:

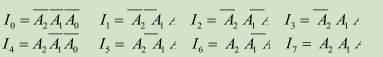

逻辑函数表达式为:

译码器的电路图如图所示:

verilog代码为:

//---------------------------------------------------------------------------

//-- 文件名 : Digital_Decoder.v

//-- 作者 : ZIRCON

//-- 描述 : 译码器模块

//-- 修订历史 : 2017-1-1

//---------------------------------------------------------------------------

module Digital_Decoder

(

/* 输入端口 */

A,

/* 输出端口 */

I

);

//---------------------------------------------------------------------------

//-- 外部端口声明

//---------------------------------------------------------------------------

input [2:0] A; //输入端口

output [7:0] I; //输出端口

//---------------------------------------------------------------------------

//-- 内部端口声明

//---------------------------------------------------------------------------

reg [7:0] I; //输出端口

//---------------------------------------------------------------------------

//-- 逻辑功能实现

//---------------------------------------------------------------------------

/* 组合电路,实现译码器 */

always @ (*)

begin

case(A)

3'b000 : I = 8'b01111111;

3'b001 : I = 8'b10111111;

3'b010 : I = 8'b11011111;

3'b011 : I = 8'b11101111;

3'b100 : I = 8'b11110111;

3'b101 : I = 8'b11111011;

3'b110 : I = 8'b11111101;

3'b111 : I = 8'b11111110;

default: I = 8'b11111111;

endcase

end

endmodule

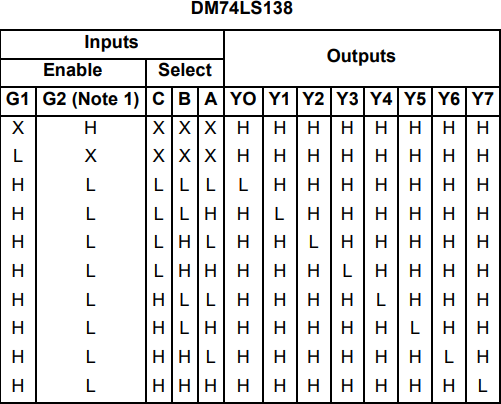

常见的3-8译码器有74LS138:

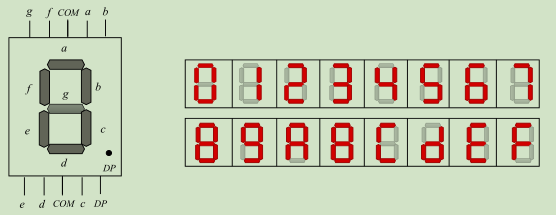

译码器的应用有七段显示译码器,数码管就为七个发光二极管,利用不同发光段的组合显示出0-9十个十进制数,驱动七段数码管显示的译码器称为BCD七段显示译码器。数码管如图所示:

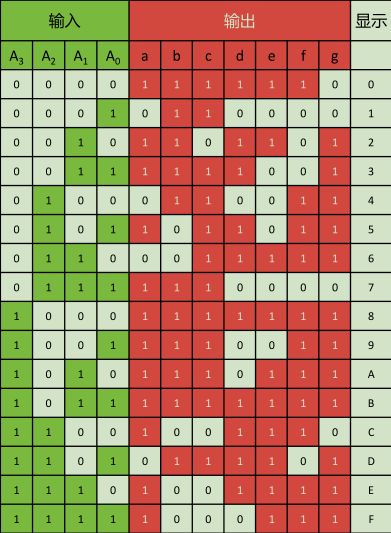

改译码器有4输入7输出,输入为待显示的BCD码,输出接到七段数码管的对应接线端,真值表如图所示:

输入信号为0000时,输出为abcdefg = 1111110,点亮的abcdefg发光二极管刚好显示为0。

3.2.3、数据选择器

数据选择器就是从多个输入的逻辑信号中选择一个逻辑信号输出,数据选择器也被称为多路复用器,相当于多个输入的单刀多掷开关。

以8-1数据选择器为例,功能示意图如图所示:

译码器的输出控制8个开关的通断,8-1数据选择器的真值表如图所示:

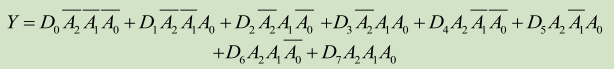

逻辑表达式为:

verilog代码为:

//---------------------------------------------------------------------------

//-- 文件名 : Digital_Selector.v

//-- 作者 : ZIRCON

//-- 描述 : 选择器模块

//-- 修订历史 : 2017-1-1

//---------------------------------------------------------------------------

module Digital_Selector

(

/* 输入端口 */

A,D0,D1,D2,D3,D4,D5,D6,D7,

/* 输出端口 */

Y

);

//---------------------------------------------------------------------------

//-- 外部端口声明

//---------------------------------------------------------------------------

input D0,D1,D2,D3,D4,D5,D6,D7; //输入端口

input [2:0] A; //输入端口

output [7:0] Y; //输出端口

//---------------------------------------------------------------------------

//-- 内部端口声明

//---------------------------------------------------------------------------

reg [7:0] Y; //输出端口

//---------------------------------------------------------------------------

//-- 逻辑功能实现

//---------------------------------------------------------------------------

/* 组合电路,实现选择器 */

always @ (*)

begin

case(A)

3'b000 : Y = D0;

3'b001 : Y = D1;

3'b010 : Y = D2;

3'b011 : Y = D3;

3'b100 : Y = D4;

3'b101 : Y = D5;

3'b110 : Y = D6;

3'b111 : Y = D7;

default: Y = 1'b0;

endcase

end

endmodule

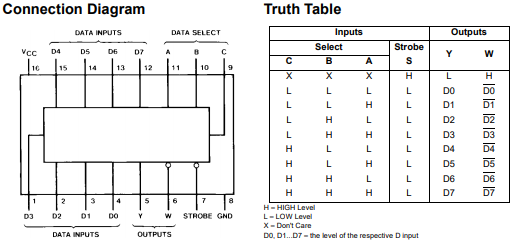

常见的8-1数据选择器有74LS151,真值表如图所示:

参考:锆石教程

最后

以上就是义气高山最近收集整理的关于数字电路篇三的全部内容,更多相关数字电路篇三内容请搜索靠谱客的其他文章。

发表评论 取消回复