一、同步复位

定义:从名字来看,同步也就是和时钟同步的关系,一起发生变化。所以同步复位就是只有时钟上升沿到来时,才能产生有效变化;否则,无法产生对系统的复位操作。举个例子如下:

//一个高电平有效的同步复位的D触发器

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk)begin

if(reset)

q <= 8'd0;

else

q <= d;

end

endmodule对应的仿真代码如下

`timescale 1ns / 1ps

module fang( );

reg clk,reset;

reg [7:0]d;

wire [7:0]q;

initial begin

clk = 0;

reset = 1;

#60

reset = 0;

#20 reset = 1;

end

initial begin

d = 1;

#20 d=2;

end

always #10 clk = ~clk;

top_module u1(

.clk(clk),

.reset(reset),

.d(d),

.q(q)

);

endmodule

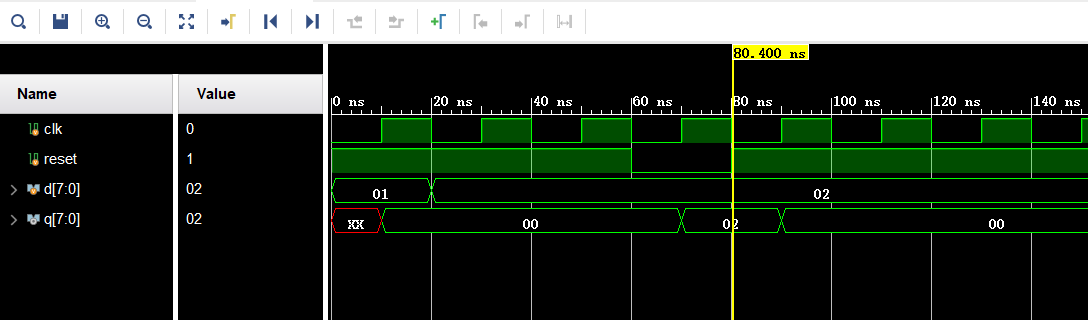

最重要的时序图如下:

从图中可以看到,0ns我们设置的是已经复位,但输出并没有为0,知道等到10ns的第一个时钟沿到来,才输出为0,由此可以得知,只有时钟沿到来时,复位才有效果;后面的60到80ns已经不复位,但只有等到70ns的时钟沿到来时,才输出d的值同理。

-

优点:

- 一般能够确保电路是百分之百同步的;

- 确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段;

-

缺点:

- 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位。同时还要考虑如:时钟偏移、组合逻辑路径延时、复位延时等因素;

- 由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源;

二、异步复位

定义:即无论时钟边沿到来与否,只要复位信号有效输出就会被复位。(与时钟没有关系)

module top_module (

input clk,

input rst_n, // Synchronous reset

input [7:0] d,

output reg [7:0] q

);

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

q <= 8'd0;

else

q <= d;

end

endmodule对应的仿真代码如下:

`timescale 1ns / 1ps

module fang( );

reg clk,rst_n;

reg [7:0]d;

wire [7:0]q;

initial begin

clk = 0;

rst_n = 0;

#60

rst_n = 1;

#20 rst_n = 0;

end

initial begin

d = 1;

#20 d=2;

end

always #10 clk = ~clk;

top_module u1(

.clk(clk),

.rst_n(rst_n),

.d(d),

.q(q)

);

endmodule

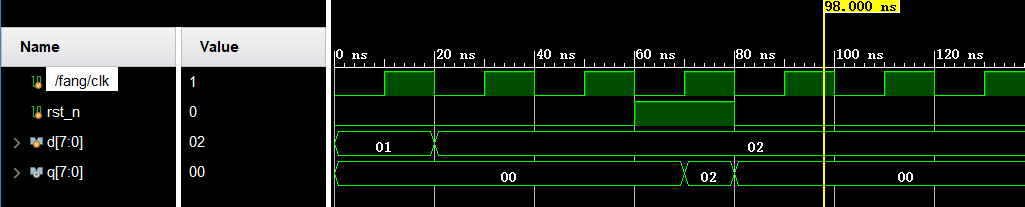

时序图如下

从图中可以看到,只要复位为0,q的值就为0,与时钟没有关系;而当不为0时,则是在不复位的下一个时钟沿进行赋值。

-

优点:

-

大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。

-

设计相对简单。

-

异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

-

缺点:

-

在复位信号释放(release)的时候容易出现问题。具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致亚稳态。(可以百度百科,里面介绍很详细,主要就是说变化时间反应不过来,经典解决方法就是双触发)

-

复位信号容易受到毛刺的影响

总结:所以,综述,一般都推荐使用异步复位,同步释放的方式,而且复位信号低电平有效。所谓异步复位,同步释放就是在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。

三、异步复位,同步释放

module top_module (

input rst_n,

input clk,

output rst_syn_n;//系统的复位信号

);

reg reg1,reg2;

always@(posedge clk or negedge rst_n )begin

if(!rst_n)begin

reg1<=1'b0;

reg2<=1'b0;

end

else begin

reg1<=1'b1;

reg2<=reg1;

end

end

assign rst_syn_n = reg2;

endmodule复位是异步的,但是释放确实同步的;用两级寄存器,是消除复位释放中可能存在的亚稳态。

异步复位,同步释放的好处是:

1.不要求复位信号必须大于一个时钟周期;

2.因为释放过程和时钟同步,所以避免了亚稳态。

兼具同步复位和异步复位的优点。

不使用reg1的原因是消除毛刺的影响,如果受到毛刺的影响,reg1会产生一个很短的复位信号,这样可能会导致复位不完全,系统出现混乱。

完结!

最后

以上就是迷人裙子最近收集整理的关于FPGA学习(一)同步复位和异步复位的区别一、同步复位二、异步复位三、异步复位,同步释放的全部内容,更多相关FPGA学习(一)同步复位和异步复位内容请搜索靠谱客的其他文章。

发表评论 取消回复