上次芯动面试官问到了这个问题,回答的比较草率,这次把这个问题总结一下

首先分析一下什么是异步复位,同步复位

同步复位:只有在时钟沿到来时复位信号才起作用。

缺点是复位信号持续的时间应该超过一个时钟周期才能保证系统复位

异步复位:复位信号与时钟沿是否到来无关。

缺点是复位信号容易受到毛刺的影响。并且如果复位结束时刻恰在亚稳态窗口内时,就无法正常复位

所以为了避免同步复位和异步复位的缺点,就产生了一种“异步复位同步释放”的复位方式

异步复位同步释放:

当异步复位有效时,复位信号立刻复位

信号释放时,会在时钟上升沿来临时,才可以恢复

用一个例题来看看代码实现:使用异步复位同步释放来将输入数据a存储到寄存器中

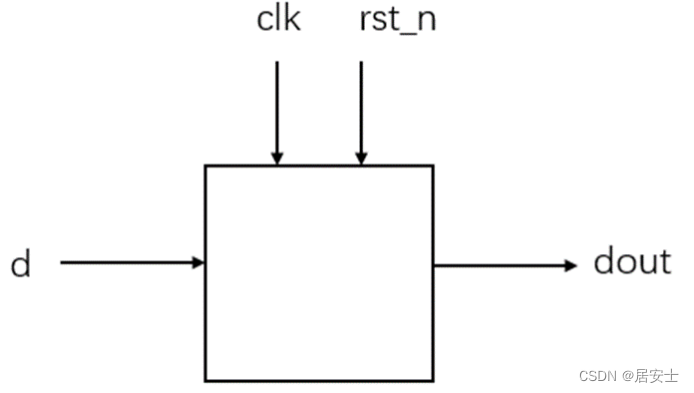

clk为时钟,rst_n为低电平复位,d信号输入,dout信号输出

步骤是:

(1)设计2个复位寄存器rst0,rst1

(2)当有复位信号的时候,rst=1,rst=0需要在clk上升沿,再把rst0赋给rst1(打拍避免亚稳态)

(2)数据输出时复位信号选择rst1

代码如下:

`timescale 1ns/1ns

module ali16(

input wire clk,

input wire rst_n,

input wire d,

output reg dout

);

reg rst0,rst1;//定义2个复位信号寄存器

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

rst0 <= 0;

rst1 <= 0;

end

else begin

rst0 <= 1; //异步复位

rst1 <= rst0; //同步释放

end

end

always @ (posedge clk or negedge rst1)begin//数据输出的时候用新的复位信号

if(!rst1) begin

dout <= 1'b0;

end

else begin

dout <= d;

end

end

endmodule 最后

以上就是悲凉背包最近收集整理的关于FPGA 异步复位同步释放 详解的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复